深圳国际量子研究院贺煜课题组在硅基量子计算领域实现重要突破

近日,在俞大鹏院士的带领下,深圳国际量子研究院贺煜研究员课题组在硅基量子计算领域取得重要突破。研究团队在原子级精度加工的硅基量子计算芯片上,首次成功演示了与容错量子计算架构兼容的基于稳定子的量子错误探测,并直接揭示了硅基自旋量子比特系统中的强偏置噪声特性。相关成果以“Quantum error detection in a silicon quantum processor”为题于2026年1月26日在国际高水平期刊 Nature Electronics 上在线发表。

量子错误探测与纠正是构建大规模容错量子计算机的核心前提。硅基自旋量子比特因其与现有半导体工艺兼容、相干时间长、可大规模扩展等优势,被认为是构建通用量子计算机最具潜力的平台之一。近年来,该领域在量子比特数目、量子门保真度以及读出保真度等方面取得了一系列重要突破。此前国际上的研究虽然实现了基于三个自旋量子比特的相位翻转纠错的初步演示,但是与表面码等容错架构兼容的稳定子探测在硅基系统中尚未实现。

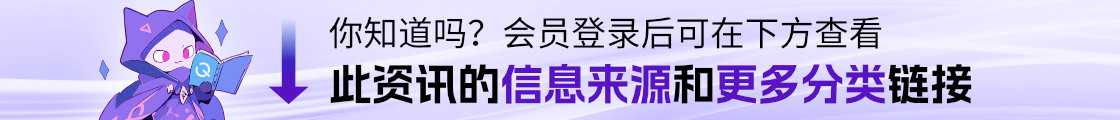

面对这一挑战,研究团队利用扫描隧道显微镜氢掩模直写技术,制备了原子级精度的硅基量子处理器。该芯片包含用于自旋读取的单电子晶体管、由磷原子团簇构成的三个量子点、控制栅极以及用来施加脉冲信号的微波天线。研究团队利用电子自旋共振 (ESR) 和核磁共振 (NMR) 等技术对其中的一个量子点(最右侧)进行了能谱表征(如图1),确认其包含5个磷原子核,1个邻近的氢原子核以及 1个电子。在本研究中使用了其中4个磷原子核自旋以及1个电子自旋比特 (其他两个原子核被初始化) 来执行量子计算线路。

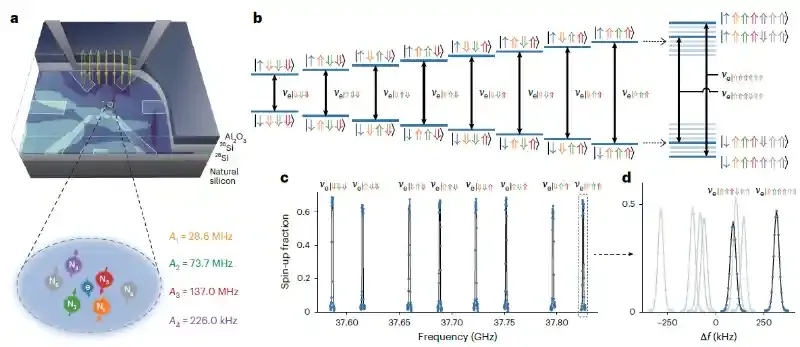

实验上,主要用量子点中的原子核自旋作为编码比特,电子自旋作为辅助比特。该芯片的核心特色在于利用共享的电子作为媒介,实现了所有核自旋之间的全连通耦合。在基本量子门表征方面,该芯片实现了平均保真度达99.57%的单比特Clifford门,以及平均保真度约97.76%的两比特CZ门。基于此,团队利用原生的单比特门以及CCCZ门高效地构建了多比特的Toffili门,通过态转移矩阵的表征办法证明其保真度达到95.9%,这些关键的量子门为后续高保真量子线路的执行提供了必要的工具包。凭借这一高连通性架构,研究团队成功地在所有核自旋对间制备了平均保真度为93.4%的Bell纠缠态,并进一步生成了保真度为88.5%的四比特GHZ态,该数值刷新了硅基体系的最高纪录,充分验证了硅基磷原子处理器在制备和操控多体量子纠缠的能力。

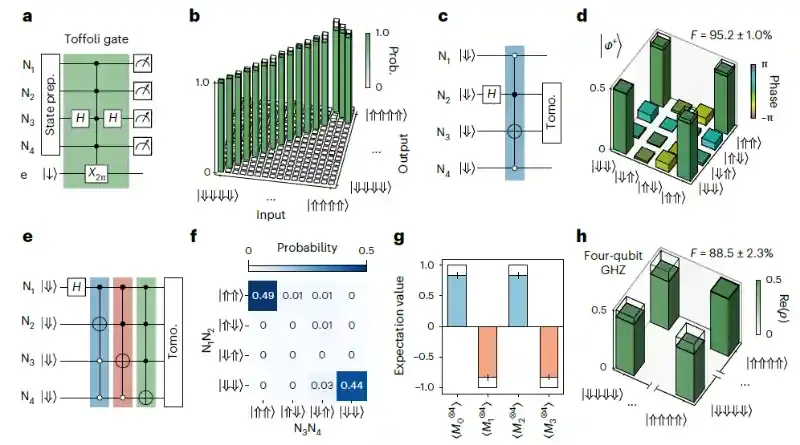

研究团队通过设计的四量子比特错误探测电路,实现了[[2, 0, 2]]编码,利用 (SX = XX) 和 (SZ = ZZ) 两个稳定子,以量子非破坏性测量 (QND)的方式,成功实现了对编码比特中发生的任意单比特错误的高效检测。同时,本研究通过延长等待时间引入退相干过程,展示了即使在量子比特发生部分退相干的情况下,纠缠信息仍能被有效地通过纠错得到恢复(数据后处理),验证了该错误检测方案的有效性与鲁棒性。

此外,本研究在国际上首次在硅基量子比特系统中利用基于稳定子测量的办法直接观测到强偏置噪声的特征,即系统退相干为主要误差来源,而非弛豫过程。这一物理特性为未来设计针对硅基自旋系统的低开销、高效率容错量子计算编码方案提供了关键实验依据。

在该研究工作中,张春辉(国量院/南科大博士研究生)、李春晖(国量院/南科大博士研究生)、田振(国量院助理研究员)为论文共同第一作者。贺煜研究员、俞大鹏院士、胡光冲副研究员、王观勇副研究员为论文通讯作者。该研究工作得到了国家自然科学基金委、合肥国家实验室、深圳市科技创新局、广东省科技厅等单位的资助与支持。