面向高效量子计算的三比特门实现

量子计算理论显示,所有量子计算任务都可以分解为两比特门和单比特旋转门这样的基本量子操作,这样两比特门和单比特旋转门就构成通用量子计算的基本逻辑门,对应于经典计算中的“或、与、非”等逻辑门。通常,复杂的量子算法由作用在多个量子比特上的大规模量子线路实现,包含有大量基本逻辑门操作。在这种情况下,三量子比特门在量子计算中就由多个两比特门和单比特门组合而成。

实际上,诸多的量子算法必然会出现大量的三比特门,如果能提供三比特门的直接硬件实现,将大大提升量子计算的效率,并简化量子线路,提升保真度,原因是三比特门由多个单比特和双比特门的串联组合构成,这种基于分解的方法将显著增加量子电路的深度,导致操作时间延长、误差累积加剧以及退相干效应增强,难以满足大规模量子处理器对门操作精度与效率的严格要求。尤其是在当前含噪中等规模量子(NISQ)时代,构建保真度高、结构紧凑且可扩展性强的三比特门成为推动量子计算发展的关键课题。

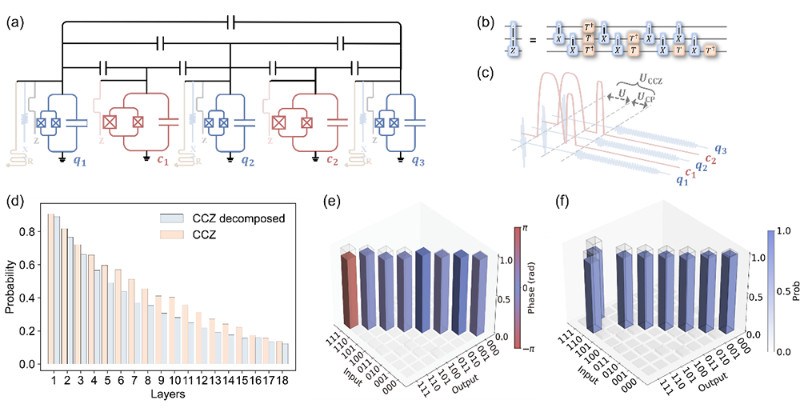

中国科学院物理研究所/北京凝聚态物理国家研究中心超导量子计算团队利用自主研发的基于倒装焊技术,集成有多个量子比特的超导量子处理器,提出并实现了新型三比特Controlled-Controlled-Z(CCZ)门的直接构造方案。该方案采用可调耦合架构(图(a)),通过同时对两两近邻比特之间的可调耦合器施加精确调控的Z脉冲,在三比特间引入有效三体相互作用,再通过优化控制相位门消除近邻比特间的非目标两体相互作用,从而实现等效的三比特CCZ门(图(c))。实验结果显示,与传统分解方法实现的CCZ门(图(b))相比,该方案门时长仅需256纳秒(传统门分解方案门时长为640纳秒),并且在多层门操作后量子态泄露率显著降低(图(d)),各项指标均显著优于传统的CCZ门分解方案。利用三比特门过程层析技术,实验测得该CCZ门的平均态保真度达到97.94%,过程保真度为93.54%。通过数值模拟排除芯片退相干误差的影响后,该方案在理想条件下的态保真度可达99.5%。进一步地,研究团队基于该CCZ门构建了Toffoli门,验证其作为通用量子计算单元的可行性;通过成功演示三比特Grover量子搜索算法,系统验证门操作的实用化潜力。这项研究首次在可扩展的多比特超导量子处理器上实现了直接的高性能三比特门操作,为未来多体量子门的设计与量子算法的高效执行提供了重要的实验平台和技术路径。

相关成果以“Direct Implementation of High-Fidelity Three-Qubit Gates for Superconducting Processor with Tunable Couplers”为题发表于 Physical Review Letters 135, 050602 (2025),并被遴选为当期的封面文章。物理所博士生刘皓天、陈炳杰为该研究的共同第一作者;时运豪博士后、许凯副研究员和范桁研究员为共同通讯作者,作者还包括物理所郑东宁研究员、宋小会副研究员、相忠诚副主任工程师等。本工作受到国家自然科学基金项目、量子科技创新计划、北京市科技新星计划和中国科学院的资助。