通用光子逻辑张量计算芯片

近日,华中科技大学武汉光电国家研究中心张新亮、董建绩研究团队联合中国科学院上海技术物理研究所胡伟达研究员,提出新型光子逻辑张量计算架构,并研制出单核算力超Tbit/s的可重构光子逻辑芯片。该成果突破了传统光子逻辑门并行性不足、重构能力差的限制,发表在学术期刊《Optica》上,论文题为“Photonic logic tensor computing beyond Tbit/s per core”。

逻辑门是现代数字计算系统的基础组件。随着人工智能和通信行业的快速发展,现有电子数字计算架构面临功耗高、带宽受限等瓶颈。相比之下,光子计算因其低延迟、高带宽和天然并行性,成为突破“摩尔定律”瓶颈的有力候选之一。然而,现有光子逻辑架构因受限于较弱非线性效应,难以实现高并行性和可重构操作,无法突破大规模扩展并走向实用。

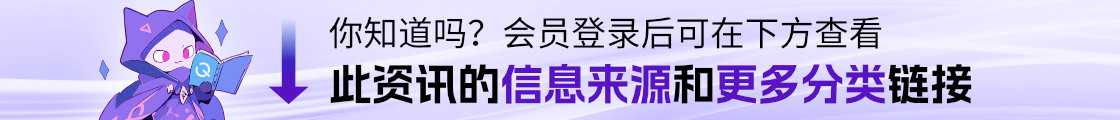

为解决这一难题,研究团队提出了一种新型光子逻辑张量计算架构,并构建了首个光子通用逻辑张量核(PULTC)。该芯片将电信号通过大带宽微环调制器进行非线性映射至光载波上,借助马赫-曾德尔干涉仪(MZI)阵列完成高维线性变换,从而实现任意的逻辑功能。在实验中,芯片集成了10个波长通道和4个空间通道,每个通道的逻辑计算速率可达50 Gbit/s,总计算能力超过1 Tbit/s,理论上可扩展至40 Tbit/s。其结构如图1所示:

该芯片具有以下技术优势:1)高并行、高通量逻辑运算,空间与波长两个维度相组合使得芯片能同时执行m×n个逻辑并行操作,大幅提升芯片算力;2)可重构逻辑功能,通过可编程的MZI阵列实现任意布尔逻辑运算,针对两输入信号展示了16种逻辑输出可能性;3)超低功耗设计,理论功耗仅为1.5 fJ/bit,在相同计算速率下将显著优于传统CMOS逻辑门;

在系统应用方面,研究团队联合重庆CUMEC公司,开发了基于PULTC芯片的逻辑张量计算板卡,如图2所示。该板卡包含PCIe和Ethernet接口,主控FPGA集成高速信号发射和接收模块,实现数据一体化收发;配置低速DAC阵列为芯片提供偏压,用来维持芯片工作状态稳定;采用SDRAM,对光计算芯片产生的高速数据流即时存储;集成PD阵列,可在板卡内完成光信号的采集。研究团队展示了该板卡多场景的应用能力,包括多位宽加减乘除四则运算、元胞自动机演化、图像加密与解密、图像边缘提取,展现出光学数字计算的通用性。该成果充分利用了光在并行计算与计算能效方面的天然优势,通过架构创新与片上集成,向大规模通用光数字计算系统迈出了重要一步。未来,该架构有望在AI加速、边缘计算、光逻辑神经网络等领域得到广泛应用。

该研究得到国家重点研发计划项目支持。张文凯博士为论文第一作者,周海龙教授、胡伟达研究员、董建绩教授为论文共同通讯作者。