深圳国际量子研究院超导团队在量子纠错领域取得重要突破

近日,深圳国际量子研究院俞大鹏院士团队与中国科学院计算技术研究所孙晓明研究员团队合作,在量子纠错与容错量子计算方向取得重要突破。合作团队在超导量子芯片上,基于Floquet-Bacon-Shor纠错码,在成功编码传统“静态逻辑比特”的基础上,额外编码了“动态逻辑比特”,演示了两比特逻辑态的保持和操作,并通过逻辑受控非门(CNOT门)实现了两种逻辑比特间的高保真度纠缠。相关成果以“Logical Operations with a Dynamical Qubit in Floquet-Bacon-Shor Code”为题,于2025年11月25日在线发表在国际顶级物理学期刊Physical Review Letters。

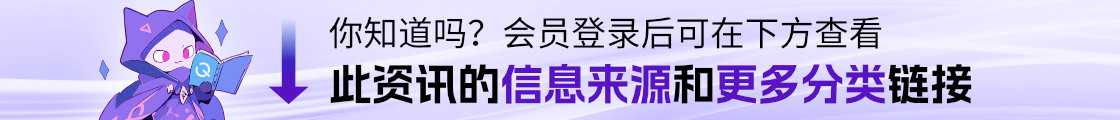

量子计算机有望在若干复杂问题上超越经典计算,但量子态极其脆弱,必须依靠量子纠错进行保护。传统的稳定子纠错码(如表面码、色码、Bacon-Shor码等)通过在多物理比特上冗余编码,并反复执行稳定子测量,实现对错误的探测与抑制,近年在多种物理体系上已取得重要进展。然而,这类方案一般将逻辑信息固定编码在一个随时间不变的子空间中,逻辑比特本身是“静态”的。近年来提出的时间动态量子纠错新思路,如Floquet码及其广义实现方案,则通过在时间维度上引入周期性的低权重奇偶校验测量,让编码结构随时间演化,从而在同一套物理资源中编码出额外的“动态逻辑比特”,提升编码灵活性和潜在纠错性能,为实现更为资源高效的容错量子计算提供了新的可能。

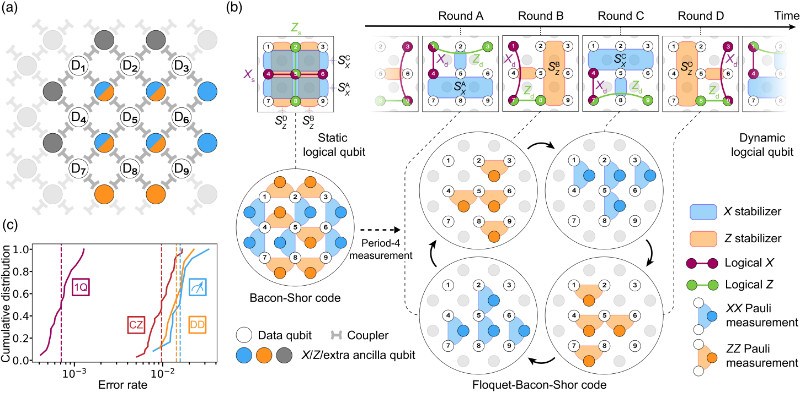

在此项研究中,研究团队在一块66比特超导量子芯片上,选取其中21个比特实现了Floquet-Bacon-Shor(FBS)码。该编码基于一个 3×3 数据比特方阵及其周围的辅助比特,是一种码距为2、仅需四方格晶格连通性的Floquet码实现形式。相较于只编码一个静态逻辑比特的传统Bacon-Shor码,FBS码在保持静态逻辑比特的同时,通过对权重为2的Pauli测量施加周期为4的时间调度,在规范自由度中额外编码出一个动态逻辑比特,从而在同一物理结构上形成一对静态和动态逻辑比特。实验中,团队成功制备了全部36种两比特逻辑Pauli本征态,并通过逻辑量子态层析对其进行表征;其中一部分逻辑态采用容错方案制备,表现出更高的编码保真度。通过多轮稳定子测量进行错误探测和筛选,研究人员实现了对两比特逻辑态的稳定保持:以逻辑态 ∣−,0⟩ 和 ∣−,1⟩ 为例,每轮原始逻辑错误率约为14%,引入错误探测后则降至约2.6%每轮,显著优于相同时间尺度下的物理错误水平。

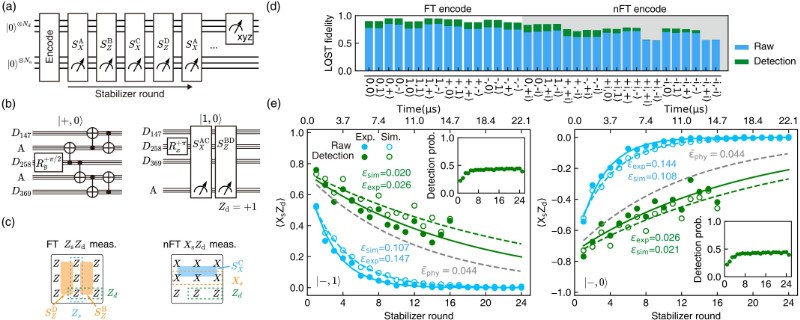

在实验过程中,团队还对逻辑层面的操作能力进行了系统研究,涵盖单比特逻辑门和两比特逻辑门。针对动态逻辑比特,研究人员在稳定子测量轮之间插入横向单比特门,实现了容错的逻辑Pauli门,其在多种输入逻辑态上的平均保真度与不插入门时基本持平,说明该类门操作在错误探测框架下几乎不引入额外逻辑错误。此外,团队利用辅助比特构造了围绕不同轴向的任意角度旋转门,并通过测量逻辑算符期望值随旋转角度的变化,验证了其与理论预期的一致性。在此基础上,研究人员设计并实现了静态逻辑比特对动态逻辑比特的逻辑受控非门,通过该门将初态 ∣+,0⟩ 演化为一对逻辑比特之间的Bell纠缠态。利用错误探测后得到的逻辑Bell态保真度为75.9%,逻辑过程层析给出的逻辑CNOT门保真度约为84.1%,在剔除部分本身编码质量较低的输入态后,估算门保真度可达约93.6%。这些结果表明,在超导量子芯片上采用Floquet-Bacon-Shor码,能够在量子纠错保护下实现静态与动态逻辑比特的联合编码、保持及高质量逻辑操作,为未来面向更大规模、资源更高效的容错量子计算奠定了重要实验基础。

图4. 动态和静态逻辑比特间的CNOT门与逻辑Bell态

在该研究工作中,孙炫东(国量院博士研究生)、李龙成(中国科学院计算技术研究所硕士研究生、现剑桥大学博士研究生)、吴智艺(北京大学物理学院博士研究生、国量院访问学生)为论文共同第一作者。俞大鹏、孙晓明、钟有鹏、储继为通讯作者,俞大鹏院士为最后作者。该研究工作得到了广东省科技厅、深圳市科创局、国家自然科学基金委、合肥国家实验室等单位的大力支持。