高维空间模式量子逻辑门三维光子集成芯片研究重要进展

近日,华中科技大学武汉光电国家研究中心王健教授领导的多维光子学实验室(Multi-Dimensional Photonics Laboratory, MDPL)团队在高维空间模式量子信息处理光子集成芯片领域取得新进展,相关研究成果以 Ultra-compact 3D integrated photonic chip for high-fidelity high-dimensional quantum gates 为题,发表在国际学术期刊《Science Advances》上。

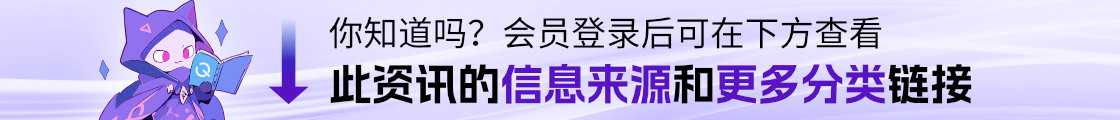

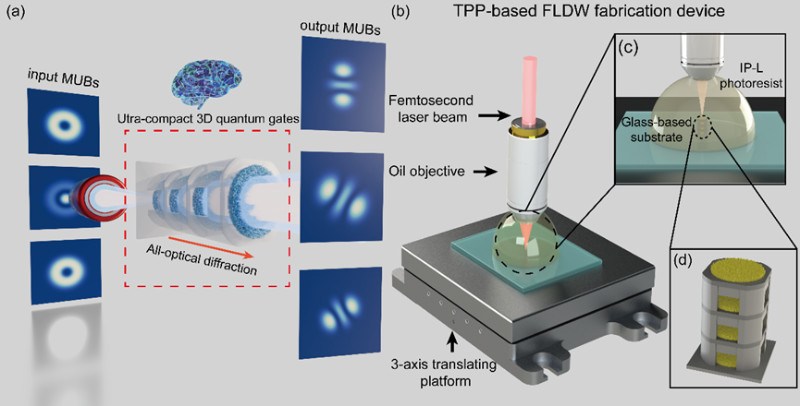

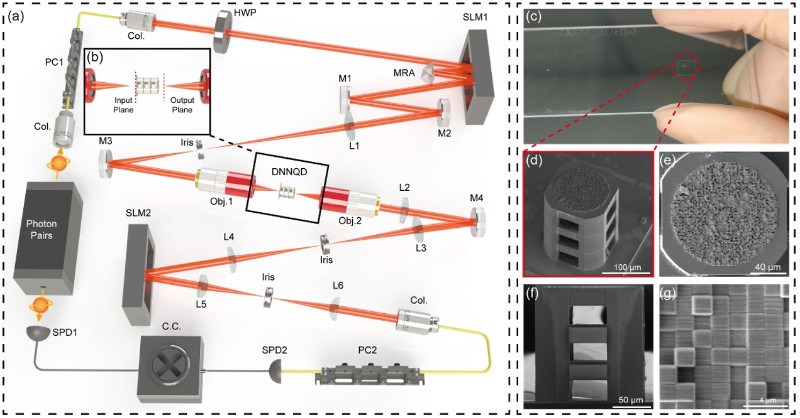

该研究基于空间衍射神经网络(Diffractive Neural Network, DNN)多平面光转换(MPLC)技术,发展了一种聚合物基MPLC三维光子集成芯片,用于在光子的空间模式自由度中实现高维量子逻辑门(图1)。该芯片采用双光子聚合飞秒激光直写(femtosecond laser direct writing, FLDW)技术在聚合物材料中制备而成,整体结构紧凑,具备微米级加工精度,适用于集成化和小型化应用场景。研究团队设计并实现了一个三维Hadamard量子门结构,并在单光子水平上进行了空间模式下的量子过程层析,实验测得的保真度为90%。

光子的空间模式具有理论无限维的正交基底,这为高维量子信息编码提供了丰富资源。在众多实现方式中,MPLC技术凭借其多相位面波前调控能力,同时结合DNN智能设计方法,被广泛应用于空间模式转换及其在光通信、成像和计算中的拓展。传统的MPLC系统多依赖于空间光调制器(SLM)和多次反射镜等实现,存在体积大、器件结构复杂、对准要求高等局限。该研究工作通过聚合物材料微结构加工,成功实现了四层MPLC结构的紧凑集成,其功能依托于神经网络辅助设计的衍射光场转换过程,具备高精度光场调控能力。

在三维光子集成芯片设计和加工过程中,研究团队利用DNN对各相位面的分布进行了训练与优化,并通过三维打印技术制备出芯片。该芯片的结构特征尺寸为1.6 μm,在保证紧凑性的同时,具备对单光子空间模式的有效操控能力(图2)。实验中,团队采用三维空间模式下的量子过程层析技术对芯片性能进行了评估,获得了90%的保真度,验证了该方法在空间模式量子门构建中的可行性与良好性能(图3)。

研究中还对芯片性能的影响因素进行了分析,指出在保持芯片完整性的前提下开发高效的测试方法将有助于进一步提升性能。此外,研究还指出,面向更复杂的三维及高维量子门应用,聚合物MPLC芯片具备进一步拓展空间,包括增加光相位面数量与像素密度等方向。

该工作展示了一种结合飞秒激光微纳制造与神经网络优化设计的新路径,在光子空间模式下实现了高维量子门的紧凑实现,为构建集成化、高精度量子逻辑操作平台提供了新技术方案。研究结果为后续空间模式量子计算平台的小型化、可集成化设计提供了实验依据与技术基础。

该工作于2025年7月5日发表在《Science Advances》上,华中科技大学武汉光电国家研究中心为论文第一单位,博士生王康睿、博士生吕大为和博士后蔡丞坤为论文共同第一作者,王健教授和刘俊副教授为论文共同通讯作者。